Tipos de Flip-Flop

Flip-Flop

Siendo los Flip-Flop las unidades básicas de todos los sistemas secuenciales, existen cuatro tipos: el RS, el JK, el T y el D. Y los últimos tres se implementan del primero —pudiéndose con posterioridad con cualquiera de los resultados confeccionar quienquiera de los restantes.

Todos pueden ser de dos tipos, a saber: Flip-Flop activado por nivel (FF-AN) o bien Flip-Flop maestro-esclavo (FF-ME). El primero recibe su nombre por actuar meramente con los "niveles" de amplitud 0-1, en cambio el segundo son dos FF-AN combinados de tal manera que uno "hace caso" al otro.

Un circuito flip-flop puede mantener un estado binario indefinidamente (Siempre y cuando se le este suministrando potencia al circuito) hasta que se cambie por una señal de entrada para cambiar estados. La principal diferencia entre varios tipos de flip-flops es el numero de entradas que poseen y la manera en la cual las entradas afecten el estado binario.

Circuito básico de un flip-flop

Se menciono que un circuito flip-flop puede estar formado por dos compuertas NAND o dos compuertas NOR. Estas construcciones se muestran en los diagramas lógicos de las figuras. Cada circuito forma un flip-flop básico del cual se pueden construir uno mas complicado. La conexión de acoplamiento intercruzado de la salida de una compuerta a la entrada de la otra constituye un camino de retroalimentación. Por esta razón, los circuitos se clasifican como circuitos secuenciales asincrónicos. Cada flip-flop tiene dos salidas, Q y Q´ y dos entradas S (set) y R (reset). Este tipo de flip-flop se llama Flip-Flop RS acoplado directamente o bloqueador SR (SR latch). Las letras R y S son las iniciales de los nombres en inglés de las entradas (reset, set).

Circuito flip-flop básico con compuertas NOR

Para analizar la operación del circuito de la figura anterior se debe recordar que la salida de una compuerta NOR es 0 si cualquier entrada es 1 y que la salida es 1 solamente cuando todas las entradas sean 0. Como punto de partida asúmase que la entrada de puesta a uno (set) es 1 y que la entrada de puesta a 0 (reset) sea 0. Como la compuerta 2 tiene una entrada de 1, su salida Q´ debe ser 0, lo cual coloca ambas entradas de la compuerta 1 a 0 para tener la salida Q como 1. Cuando la entrada de puesta a uno (set) vuelva a 0, las salidas permanecerán iguales ya que la salida Q permanece como 1, dejando una entrada de la compuerta 2 en 1. Esto causa que la salida Q´ permanezca en 0 lo cual coloca ambas entradas de la compuerta número 1 en 0 y así la salida Q es 1. De la misma manera es posible demostrar que un 1 en la entrada de puesta a cero (reset) cambia la salida Q a 0 y Q´ a 1. Cuando la entrada de puesta a cero cambia a 0, las salidas no cambian.

Cuando se aplica un 1 a ambas entradas de puesta a uno y puesta a cero ambas salidas Q y Q´ van a 0. Esta condición viola el hecho de que las salidas Q y Q´ son complementos entre si. En operación normal esta condición debe evitarse asegurándose que no se aplica un 1 a ambas entradas simultáneamente.

Un flip-flop tiene dos entradas útiles. Cuando Q=1 y Q´=0 estará en el estado de puesta a uno (o estado 1). Cuando Q=0 y Q´=1 estará en el estado de puesta a cero (o estado 0). Las salidas Q y Q´ son complementos entre si y se les trata como salidas normales y de complemento respectivamente. El estado binario de un flip-flop se toma como el valor de su salida normal.

Bajo operación normal, ambas entradas permanecen en 0 a no ser que el estado del flip-flop haya cambiado. La aplicación de un 1 momentáneo a la entrada de puesta a uno causará que el flip-flop vaya a ese estado. La entrada de puesta en uno debe volver a cero antes que se aplique un uno a la entrada de puesta a cero. Un 1 momentáneo aplicado a la entrada de puesta a cero causará que el flip-flop vaya al estado de borrado (o puesta a cero). Cuando ambas entradas son inicialmente cero y se aplica un 1 a la entrada de puesta a uno o se aplica un 1 a la entrada de puesta a cero mientras que el flip-flop este borrado, quedaran las salidas sin cambio. Cuando se aplica un 1 a ambas entradas de puesta a uno y puesta a cero, ambas salidas irán a cero. Este estado es indefinido y se evita normalmente. Si ambas salidas van a 0, el estado del flip-flop es indeterminado y depende de aquella entrada que permanezca por mayor tiempo en 1 antes de hacer la transición a cero.

Circuito flip-flop básico con compuertas NAND

El circuito básico NAND de la figura anterior opera con ambas entradas normalmente en 1 a no ser que el estado del flip-flop tenga que cambiarse. La aplicación de un 0 momentáneo a la entrada de puesta a uno, causará que Q vaya a 1 y Q´ vaya a 0, llevando el flip-flop al estado de puesta a uno. Después que la entrada de puesta a uno vuelva a 1, un 0 momentáneo en la entrada de puesta a cero causará la transición al estado de borrado (clear). Cuando ambas entradas vayan a 0, ambas salidas irán a 1; esta condición se evita en la operación normal de un flip-flop.

Flip-Flop Activados por Nivel

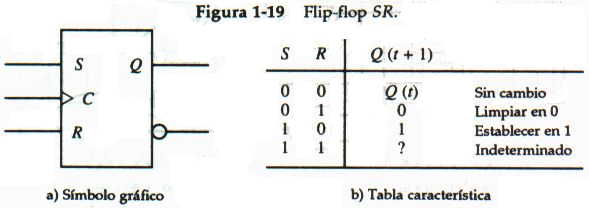

Tiene tres entradas, S (de inicio), R (reinicio o borrado) y C (para reloj). Tiene una salida Q, y a veces también una salida complementada, la que se indica con un circulo en la otra terminal de salida. Hay un pequeño triángulo en frente de la letra C, para designar una entrada dinámica. El símbolo indicador dinámico denota el echo de que el flip-flop responde a una transición positiva ( de 0 a 1) de la señal de reloj.

Su unidad básica (con compuertas NAND o NOR) se dibuja a continuación que, como actúa por "niveles" de amplitud (0-1) recibe el nombre de Flip-Flop RS activado por nivel (FF-RS-AN). Cuando no se especifica este detalle es del tipo Flip-Flop RS maestro-esclavo (FF-RS-ME). Sus ecuaciones y tabla de funcionamiento son

Q = S + q R*

R S = 0

La operación del flip-flop es como sigue. Si no hay una señal en la entrada del reloj C, la salida del circuito no puede cambiar independientemente de cuáles sean los valores de entrada de S y R. Sólo cuando la señal de reloj cambia de 0 a 1 puede la salida afectarse de acuerdo con los valores de la entrada S y R. Si S = 1 y R = 0 cuando C cambia de 0 a 1, la salida Q se inicia en 1. Si S = 0 y R = 1 cuando C cambia de 0 a 1 la salida Q se reinicia o borra en 0. Si tanto S como R son 0 durante la transición de reloj, la salida no cambia. Cuando tanto S como R son iguales a 1, la salida es impredecible y puede ser 0 o 1 dependiendo de los retrasos internos de tiempo que ocurran dentro del circuito.

Flip-flop RS temporizado

El flip-flop básico por si solo es un circuito secuencial asincrónico. Agregando compuertas a las entradas de circuito básico, puede hacerse que el flip-flop responda a los niveles de entrada durante la ocurrencia del reloj. El flip-flop RS temporizado mostrado en la siguiente figura consiste en un flip-flop básico NOR y dos compuertas NAND. Las salidas de las dos compuertas AND permanecen en cero mientras el pulso del reloj (abreviado en inglés CP) sea 0, independientemente de los valores de entrada S y R se permite llegar al flip-flop básico. El estado de puesta a uno se logra con S=1, R=0 y CP=1. Para cambiar el estado de puesta a cero (o borrado) las entradas deben ser S=0, R=1 y CP=1. Con S=1 y R=1, la ocurrencia de los pulsos de reloj causará que ambas salidas vayan momentáneamente a 0. Cuando quite el pulso, el estado del flip-flop será indeterminado, es decir, podría resultar cualquier estado, dependiendo de si la entrada de puesta a uno o la de puesta a cero del flip-flop básico, permanezca el mayor tiempo, antes de la transición a 0 al final del pulso.

Flip-flop RS temporizado

El símbolo gráfico del flip-flop RS sincronizado se muestra en la figura anterior. Tiene tres entradas: S, R y CP. La entrada CP no se describe dentro del recuadro debido a que se reconoce fácilmente por un pequeño triángulo. El triángulo es un símbolo para el indicador dinámico y denota el hecho que el flip-flop responde a una transición del reloj de entrada o flanco de subida de una señal de un nivel bajo (o binario) a un nivel alto (1 binario). Las salidas del flip-flop se marcan con Q y Q´ dentro del recuadro. Se le puede designar al flip-flop un nombre de variable diferente aunque se escriba una Q dentro del recuadro. En este caso la letra escogida para la variable del flip-flop se marca por fuera del recuadro y a lo largo de la línea de salida. El estado del flip-flop se determina del valor de su salida normal Q. Si se desea obtener el complemento de salida normal, no es necesario usar un inversor ya que el valor complementado se obtiene directamente de la salida Q´.

La tabla característica del flip-flop se muestra en la figura antes presentada. Esta tabla resume la operación del flip-flop en forma de tabulado. Q es el estado binario del flip-flop en un tiempo dado (refiriéndose al estado presente), las columnas S y R dan los valores posibles de las entradas y Q(t + 1) es el estado del flip-flop después de la ocurrencia de un pulso de reloj (refiriéndose al siguiente estado).

La ecuación característica de un flip-flop se deduce del mapa de la figura antes mencionada. Esta ecuación especifica el valor del siguiente estado como una función del presente estado y de las entradas. La ecuación característica de una expresión algebraica para la información binaria de la tabla característica. Los dos estados indeterminados se marcan con una X en el mapa, ya que pueden resultar como 1 o como 0. Sin embargo la relación SR=0 debe incluirse como parte de la ecuación característica para especificar que S y R no pueden ser iguales a 1 simultáneamente.

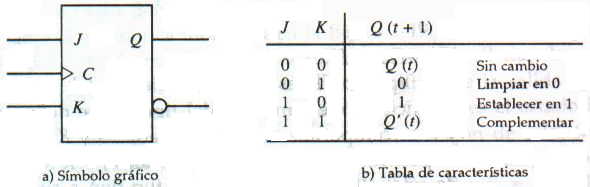

Un flip-flop JK es un refinamiento del flip-flop SR en el sentido que la condición indeterminada del tipo SR se define en el tipo JK. Las entradas J y K se comportan como las entradas S y R para iniciar y reinicia el flip-flop, respectivamente. Cuando las entradas J y K son ambas iguales a 1, una transición de reloj alterna las salidas del flip-flop a su estado complementario.

Su unidad básica se dibuja a continuación que, como actúa por "niveles" de amplitud (0-1) recibe el nombre de Flip-Flop JK activado por nivel (FF-JK-AN). Cuando no se especifica este detalle es del tipo Flip-Flop JK maestro-esclavo (FF-JK-ME). Su ecuación y tabla de funcionamiento son

Q = J q* + K* q

Se da detalle de su confección lógica a partir del FF-RS-AN.

y si simplificamos por ejemplo usando Veich-Karnaugh

R = K q

S = J q*

resulta el circuito

Flip-flop JK

Un flip-flop JK es un refinamiento del flip-flop RS ya que el estado independiente del termino RS se define en el tipo JK. Las entradas J y K se comportan como las entradas R y S para poner a uno o cero (set o reset) al flip-flop (nótese que en el flip-flop JK la entrada J se usa para la entrada de puesta a uno y la letra K para la entrada de puesta a cero). Cuando ambas entradas se aplican a J y K simultáneamente, el flip-flop cambia a su estado de complemento, esto es, si Q=1 cambia a Q=0 y viceversa.

Un flip-flop sincronizado se muestra en la figura anterior. La salida Q se aplica con K y CP a una compuerta AND de tal manera que el flip-flop se ponga a cero (clear) durante un pulso de reloj solamente si Q fue 1 previamente. De manera similar la salida Q´ se aplica a J y CP a una compuerta AND de tal manera que el flip-flop se ponga a uno con un pulso de reloj, solamente si Q´ fue 1 previamente.

Flip-flop JK temporizado

Como se muestra en la tabla característica de la figura, el flip-flop JK se comporta como un flip-flop RS excepto cuando J y K sean ambos 1. Cuando J y K sean 1, el pulso de reloj se transmite a través de una compuerta AND solamente; aquella cuya entrada se conecta a la salida del flip-flop la cual es al presente igual a 1. Así, si Q=1, la salida de la compuerta AND superior se convertirá en 1 una vez que se aplique un pulso de reloj y el flip-flop se ponga a cero. Si Q´=1 la salida de la compuerta AND se convierte en 1 y el flip-flop se pone a uno. En cualquier caso, el estado de salida del flip-flop se complementa.

Las entradas en el símbolo gráfico para el flip-flop JK deben marcarse con una J (debajo de Q) y K (debajo de Q´). La ecuación característica se da en la figura y se deduce del mapa de la tabla característica.

Nótese que debido a la conexión de retroalimentación del flip-flop JK, la señal CP que permanece en 1 (mientras que J=K=1) causará transiciones repetidas y continuas de las salidas después que las salidas hayan sido completadas. Para evitar esta operación indeseable, los pulsos de reloj deben de tener un tiempo de duración que es menor que la demora de propagación a través del flip-flop. Esta es una restricción, ya que la operación del circuito depende del ancho de los pulsos. Por esta razón los flip-flops JK nunca se construyen como se muestra en la figura. La restricción del ancho del pulso puede ser eliminada con un maestro esclavo o una construcción activada por flanco de la manera discutida en la siguiente sección. El mismo razonamiento se aplica al flip-flop T presentado a continuación.

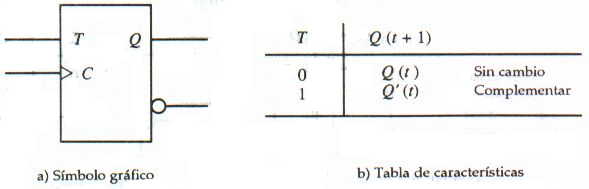

El flip-flop T se obtiene del tipo JK cuando las entradas J y K se conectan para proporcionar una entrada única designada por T. El flip-flop T, por lo tanto, tiene sólo dos condiciones. Cuando T = 0 ( J = K = 0) una transición de reloj no cambia el estado del flip-flop. Cuando T = 1 (J = K = 1) una transición de reloj complementa el estado del flip-flop.

Su unidad básica se dibuja a continuación que, como actúa por "niveles" de amplitud (0-1) recibe el nombre de Flip-Flop T activado por nivel (FF-T-AN). Cuando no se especifica este detalle es del tipo Flip-Flop T maestro-esclavo (FF-T-ME). Su ecuación y tabla de funcionamiento son

Q = T q

A partir del FF-RS-AN puede diseñarse este FF-T-AN siguiendo los pasos mostrados anteriormente, pero no tiene sentido ya que al ser activado por nivel no tiene utilidad.

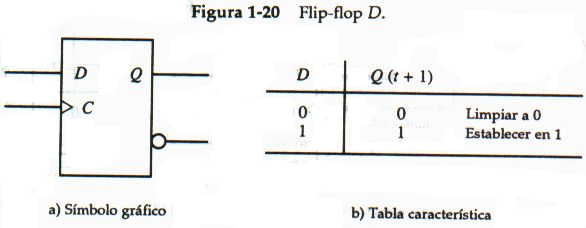

El flip-flop D (datos) es una ligera modificación del flip-flop SR. Un flip-flop SR se convierte a un flip-flop D insertando un inversor entre S y R y asignando el símbolo D a la entrada única. La entrada D se muestra durante la ocurrencia de uan transición de reloj de 0 a 1. Si D = 1, la salida del flip-flop va al estado 1, pero si D = 0, la salida del flip-flop va a el estado 0.

Su unidad básica se dibuja a continuación que, como actúa por "niveles" de amplitud (0-1) recibe el nombre de Flip-Flop D activado por nivel (FF-D-AN). Cuando no se especifica este detalle es del tipo Flip-Flop D maestro-esclavo (FF-D-ME) comúnmente denominado también Cerrojo —Latch. Su ecuación y tabla de funcionamiento son

Q = D

A partir del FF-RS-AN puede diseñarse este FF-D-AN siguiendo los pasos mostrados anteriormente, pero no tiene sentido ya que al ser activado por nivel no tiene utilidad.

Flip-flop D

El flip-flop D mostrado en la figura anterior es una modificación del flip-flop RS sincronizado. Las compuertas NAND 1 y 2 forman el flip-flop básico y las compuertas 3 y 4 las modifican para conformar el flip-flop RS sincronizado. La entrada D va directamente a la entrada S y su complemento se aplica a la entrada R a través de la compuerta 5. Mientras que el pulso de reloj de entrada sea un 0, las compuertas 3 y 4 tienen un 1 en sus salidas, independientemente del valor de las otras entradas. Esto esta de acuerdo a los requisitos de que las dos entradas del flip-flop básico NAND permanezcan inicialmente en el nivel de 1. La entrada D se comprueba durante la ocurrencia del pulso de reloj. Si es 1, la salida de la compuerta 3 va a 0, cambiando el flip-flop al estado de puesta a uno (a no ser que ya este en ese estado). Si en 0, la salida de la compuerta 4 va a 0, cambiando el flip-flop al estado de borrado.

Flip-flop D temporizado

El flip-flop tipo D recibe su nombre por la habilidad de transmitir "datos" a un flip-flop. Es básicamente un flip-flop RS con un inversor en la entrada R. el inversor agregado reduce el numero de entradas de dos a uno. Este tipo de flip-flop se llama algunas veces bloqueador D con compuertas o flip-flop de bloqueo. La entrada CP se le da a menudo la designación variable G (de gate) para indicar que esta entrada esta habilita el flip-flop de bloqueo para hacer posible que los datos entren al mismo.

El símbolo para el flip-flop D sincronizado se muestra en la figura. La tabla característica se lista en la parte (c) y la ecuación característica se lista en la parte (d). la ecuación característica muestra que el siguiente estado del flip-flop es igual a la entrada D y es independiente del valor del presente estado.

- Flip-Flop Maestro-Esclavo

Todos los cuatro FF-AN pueden implementarse siguiendo las órdenes de un FF-D-AN a su entrada como muestra el dibujo esquemático. El FF-D hace de puerta (Cerrojo). Cada pulso en el clock hará que la señal entre al sistema (como salida del FF-D-AN) y salga la misma a la salida final respetando la tabla de verdad del FF esclavo. Así, si el esclavo es un FF-X-AN, todo el conjunto se comporta como un FF-X-ME —aquí X puede ser un FF o bien también un sistema secuencial complejo.

Accesorios de los Flip-Flop

Los Flip-Flop, normalmente y si no se especifica otro detalle, son siempre Maestro-Esclavo, y suelen traer patas accesorias combinacionales. Nombramos las siguientes:

— Reset pone a cero Q

— Set pone a 1 a Q

— Clock

— Inhibición inhibe (no deja pasar) la entrada de señal

BLIBLIOGRAFIA